缓存架构

- Register 寄存器做Cache时候存储为ALU缓存Cache的指令和数据 Everything is a bit

- On Die Cache(FLC)->External Cache(MMC->LLC) Cache做Cache时候缓存Mem的Blocks Every bit is a Cache

- Memory/Virtual Memory 内存做缓存的时候缓存Disk的Pages Every cache has an address

- Swap/Disk Disk做缓存的时候缓存Net的WebPages Every address is a file

- Network Every file is energy

Specification

Cache存在的意义是为了更快的存储较慢介质中的数据

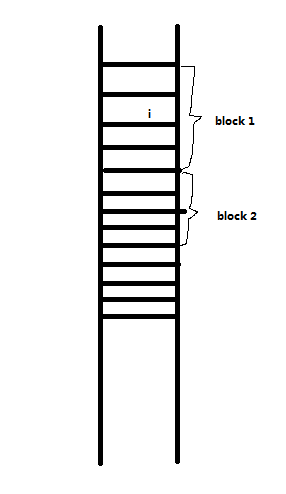

Cache有效的原因是:空间局部性和时间局部性

- 现在使用的数据很可能在不久的将来再次用到

- 现在使用的数据的周边数据很可能在不久的将来被用到

程序擅长完成直观的批量操作,例如循环可能是主要的工作

简单的循环可能会重复使用1-2个变量复杂的循环可能使用5-6个变量,这些变量很有可能存储在内存中的不同的位置。直观的说进程对内存读写造成了一些热点。

处理器的Cache基本都是硬件实现

软件工程师研究硬件的目的是为了写出更高效的软件

研究Cache可以让某些程序变快,即利用Cache的优点

研究Cache可以避免一些无法极其悲催的慢的情况,即避免Cache的缺点

专注Process Cache的形式化的存在

不关注Cache的硬件实现

Cache一个两面派

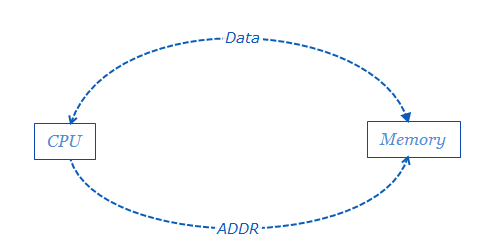

CPU是通过总线和外部设备连接的,和内存也是。地址总线给地址单向,控制总线一般是读写控制,这里没画出来,数据总线是双向的,正好对应读写。

Cache的出现对CPU的视角来说没啥影响,对Memory的视角也没什么影响。

Cache的存在是为了缩小CPU和Memory的频率的差距。

增加了速度的同时牺牲了大小。

只能放置一些常用的热点数据到Cache中,能满足大部分时间的需要。

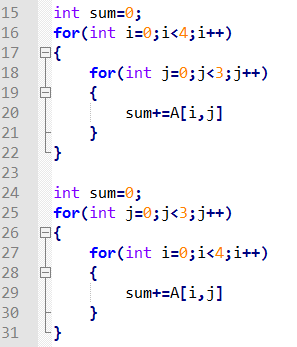

Cache友好型代码

CPU Read

Read Hit

数据在Cache中找到

Read Miss

数据在Cache中没找到

首先从内存中加载到Cache,然后从Cache中读取

策略唯一,所以说逻辑简单

CPU Write

Write Hit

要写的数据在Cache中有缓存,两种策略

Write through: Cache总是刷新内存中的block

Write Back: Cache保存要更新的Block,指导Block被Evict[驱逐]时才写到内存中

Write Miss

要写的数据不在Cache中缓存,两种策略

Write Allocate: 读取数据所在的Block到Cache中,更新Cache中的副本

Write no Allocate: 直接发送写指令到内存上,不更新Cache中的Block

CPU Write的典型策略

Write Hit的时候选择Write Back

捋一捋:CPU要修改的数据在Cache中,首先修改Cache中的Block,但是不修改内存中的Block。这需要在每个Block中设置一个Dirty Bit来标记数据block是否被修改过。

Write Miss的时候选择Write Allocate

捋一捋:CPU要修改的数据不在Cache中,首先将内存中的数据block读取到Cache中,然后更新Cache中的备份。注意这时候内存中的数据还没更新。Dirty Bit置位,表示等待更新到内存。当这个Cache Block被替换之前,再将最新的更新数据写到内存地址中。

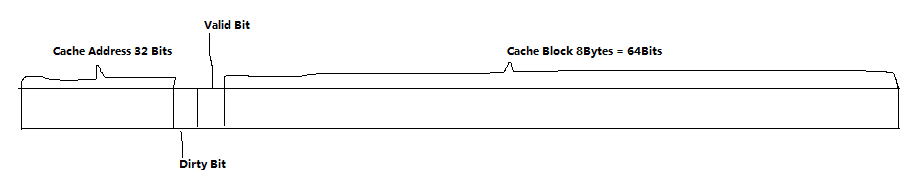

Cache Line

Cache Line是Cache的基本单元

主要有三部分组成

地址,标志位,数据Block

例如某Cache Line的参数是

- Cache Address: 32Bits,有时候后面3bits是0表示结束

- Cache Flag:

- Valid Bit : 表示这个Cache Line是否充满数据,是否可用

- Dirty Bit: 表示这个Cache Line中的数据是否需要些回到内存中,也就是说Cache Line中的数据被修改过没有。

- Cache Blocks: 8Bytes=64Bits

Fully Associate Cache Fundation

Cache Address: 32 Bits

Cache Flag: 暂时省略

Cache Blocks[B]: 64 Bytes =512Bits

Number of Cache Lines[L]: 512 Lines

Number of Sets [S]:1[全相联Cache]

Size of Cache [C]:[B]*[L]*[S]=64Bytes*512Lines=32*1024Bytes=32KBytes

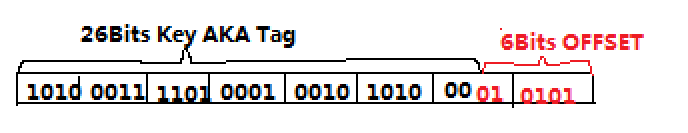

输入CPU Address可以分为下面两个部分:

第一部分是Tag,用来和Cache Address 的Tag地址对照

第二部分是OFFSET,用来寻找Bloack内部的Byte的地址

Fully Associate Cache Operation

从CPU Address中提取出Tag和Offset

比较Tag和CPU Addr中的是否一致

Match的时候

读取Cache Block,用OFFSET找到需要的Bytes发送给CPU

Not Match的时候

说明Cache中没有需要的Bytes

一般选择最近未使用的Cache Line,如果是Dirty的话,就首先写到内存中,然后发送Tag作为地址给内存,内存返回64Bytes的Data Block给Cache Line,这时候Cache Line要更新自己的Tag, Data, valid, Dirty等。最后用Offset寻找需要的Bytes发送给CPU。

Fully Associate Cache Character

传统内存的输入输出模型是:输入ADDR输出DATA BLOCK

Associate内存的输入输出模型是:输入Key 输出value,之所以这样是因为Associate模型中内存不再是地址和数据的唯一对应了,而是key-value的对应关系,key对应associate cache的tag,value对应associate的Data Block。

内存中的任意Data Block可以存放在任意Cache Line中。但是不保证所有的数据都存在在Cache中。这样的设计方便,但是全局寻找tag的时候可能比较慢。

Directed Mapped Cache Fundation

Cache Address: 32 Bits

Cache Flag: 暂时省略

Cache Blocks[B]: 64 Bytes =512Bits

Number of Cache Lines[L]: 512 Lines

Size of Cache [C]:[B]*[L]=64Bytes*512Lines=32*1024Bytes=32KBytes

Number of Sets:0[不相联Cache]

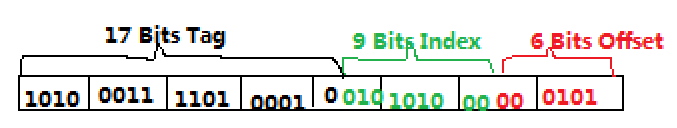

CPU Address可以分为下面三个部分

第一部分:17Bits Tag

第二部分:9 Bits Index

第三部分:6 Bits Offset

Directed Mapped Cache Operation

从ADDR Address中提取出Tag, Index, Offset

使用index定位2^9=512个Cache Line

读取出这个Cache Line

比较Addr中的Tag和Cache Line中的Tag是否一致

Same: Cache Hit,使用OFFSET去提取出需要的Bytes即可

Different: Cache Miss

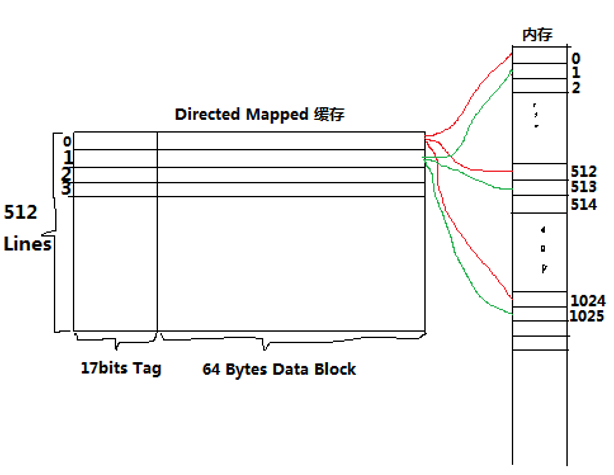

Directed Mapped Cache Character

Each Block只能被缓存到一个Cache Line里面;

例如Cache Line index=0只能缓存内存中的0,512,1024块。

如果程序循环比较大,同时使用0/512 Block中的某些Bytes,而缓存只能同时缓存一个,那么两个Block就被循环进出Cache。称为Trashing,这是我们要努力避免的现象。

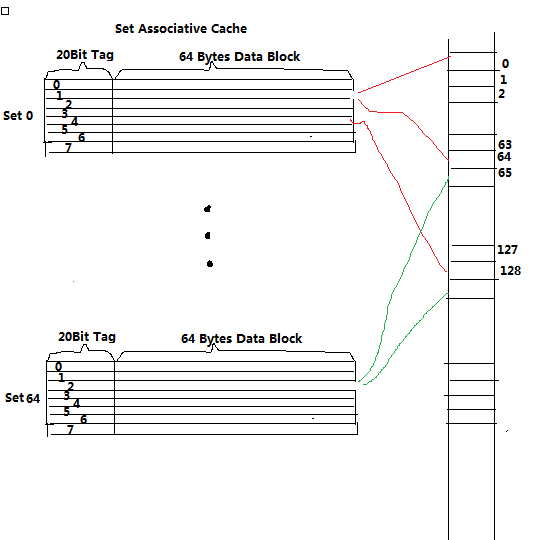

Set Associate Cache Fundation

Example:

32KBytes 8 Way Set Associative Cache

Cache Address: 32 Bits

Cache Flag: 暂时省略

Cache Blocks[B]: 64 Bytes =512Bits

Number of Cache Lines[L]: 8 Lines

Number of Sets[S]:64[全相联Cache]

Size of Cache [C]:[B]*[L]*[S]=64Bytes*8Lines*64Set=32*1024Bytes=32KBytes

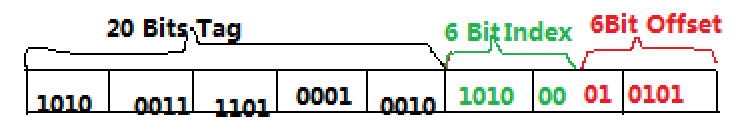

输入CPU Address可以分为下面三个部分

第一部分,20Bit Tag,用于和Cache Address的Tag对比

第二部分,6Bit Index,用于确定set,2^6=64

第三部分,6Bit Offset,用于确定data Block中的Bytes偏移

Set Associate Cache Operation

从Addr Address中提取出Tag, Index, Offset

使用index定位到Set

使用Tag看是否hit

如果Hit用Offset去寻找需要的Bytes

Set Associate Cache Character

避免了需要的某些热点数据不能同时存在于cache中的冲突现象。直观上理解最少可以保证8个热点数据存在于一个set里面

是Directed Mapped Cache和Fully Associative Cache的折中。

现实的产品级的芯片中都是采用折中策略。

参考文献

- Skylake Server Processor External Design Specification, Volume One: Architecture

- Purly Platform Snapshot

- DavidA.Patterson, JohnL.Hennessy. 计算机组成与设计硬件/软件接口[M]. 机械工业出版社, 2007.

- JohnL.Hennessy, DavidA.Patterson. 计算机体系结构量化研究方法[M]. 人民邮电出版社, 2013.

- RandalE.Bryant, DavidR.O'Hallaron. 深入理解计算机系统:a programmer's perspective[M]. 机械工业出版社, 2011.